Loading…

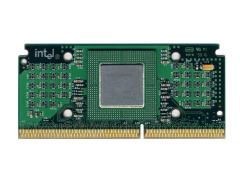

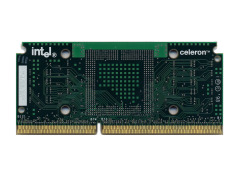

Celeron 333 MHz ES

Week 21, Year 1998CONFIDENTIAL 333/66 Q618 E A4

This engineering sample is a sample of a SECC Celeron. Built with the 0.25 µm process used for P2 Deschutes, this Celeron features an L2 cache of 128 KB and a front side bus clocked at 66 MHz. It was built in late May 1998. Intel announced the Celeron 366 on August, 24th 1999